Description

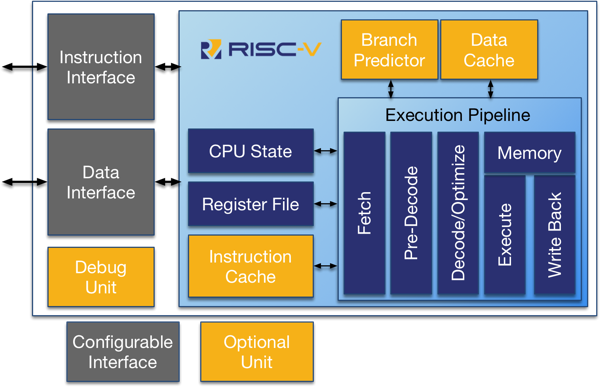

The RV12 is a highly configurable single-issue, single-core RV32I, RV64I compliant RISC CPU intended for the embedded market. The RV12 is a member of the Roa Logic’s 32/64bit CPU family based on the industry standard RISC-V instruction set

The RV12 implements a Harvard architecture for simultaneous instruction and data memory accesses. It features an optimizing folded 4-stage pipeline, which optimizes overlaps between the execution and memory accesses, thereby reducing stalls and improving efficiency.

Optional features include Branch Prediction, Instruction Cache, Data Cache, and Debug Unit. Parameterised and configurable features include the instruction and data interfaces, the branch-prediction-unit configuration, and the cache size, associativity, and replacement algorithms. Providing the user with trade offs between performance, power, and area to optimize the core for the application

RV12 Architecture

Features

High Performance 32/64bit CPU

- Royalty Free Industry standard instruction set (www.riscv.org)

- Parameterized 32/64bit data

- Fast, precise interrupts

- Custom instructions enable integration of proprietary hardware accelerators

- Single cycle execution

- Optimizing folded 4-stage pipeline

- Optional/Parameterized branch-prediction-unit

- Optional/Parameterized caches

Highly Parameterized

- User selectable 32 or 64bit data

- User selectable Branch Prediction Unit

- User selectable instruction and/or data caches

- User selectable cache size, structure, and architecture

- Flexible bus architecture supporting AHB, Wishbone

Size and power optimized design

- Fully parameterized design provides power/performance tradeoffs

- Gated clock design to reduce power

- Small silicon footprint; 30kgates for full featured implementation

Industry standard software support

- Eclipse IDE for Windows/Linux

- GNU Compiler Collection, debugger, linker, assembler

- Architectural simulator

Documentation

Datasheet

User Guide

Source Code

Download from Github